水晶振動子並みに安定なLC共振器利用のCMOSクロック発生器

水晶振動子並みの安定なクロック発生器で、CMOSチップ並みに周波数をプログラムできる。しかも位相ノイズやジッターは少ない。こんな理想的なCMOSクロック発生器を米国のファブレスベンチャーMobius Microsystems社が間もなくサンプル出荷を始める。同社製品マーケティング担当ディレクタのTunc Cenger氏がGlobalpress Connection社主催のElectronics Summit2008でその技術の詳細を明らかにした。

これまで、水晶振動子は気密封止パッケージに収容したものが多く、小型化しづらかった。最近でこそ、厚さ1mmを切る水晶振動子が出てきたが、クロック発生器として使うためにはPLL(位相ロックループ)などのICチップが必要だ。一方でシリコンプロセスを利用するMEMS振動子も最近は製品化されてきているが、今のところ1チップに集積することが難しく、2チップ構成でMCP(マルチチップパッケージ)などに実装されている。このためある程度、厚くなることはやむをえない。PLLを使って周波数を倍増していくとジッターが大きくなるという欠点もある。そこで水晶振動子の基本周波数を上げようとすると高価になる。

今回のMobiusのクロック発生器はCMOS回路でLC発振器を構成しており、分周器を使って共振周波数を落としていくという方法を使っているため、ジッターは少なくなる方向である。発振器はMEMSではなく、プレーナのLC共振器で作るため、1チップ化しやすい。これまで搭載しにくかった、フレキシブルディスプレイにも簡単に載せられる。振動や落下による影響は1個のシリコンチップに作り込むためほとんど受けない。HDD(ハードディスク装置)からSSD(半導体ディスク装置)へ可動部分をなくしてしまおうという最近のトレンドにも一致すると、Cenger氏はいう。

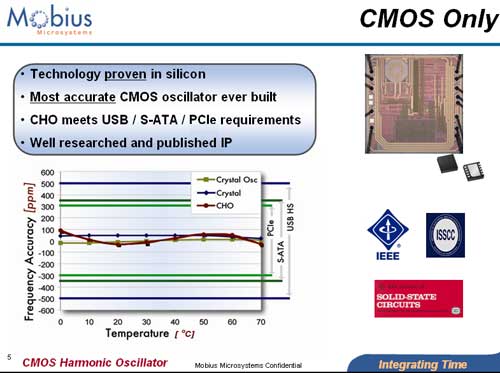

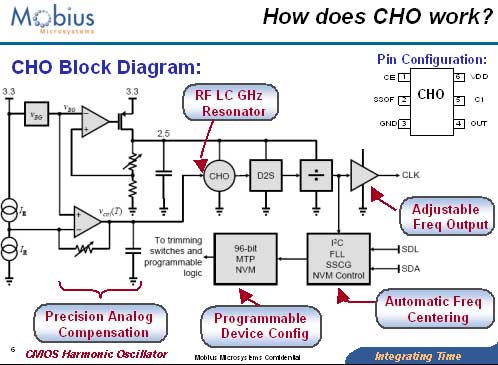

アナログCMOS回路技術を使い、今回のクロック発生器MM8511を実現したわけだが、デザインルールは0.25μm CMOS技術で、LC共振器の共振周波数は1GHz程度である。この技術を同社はCHO(CMOS Harmonic Oscillator)技術と呼んでいる。アナログ回路でもある程度微細化できるようになり、配線パターンによってインダクタンスとキャパシタンスを実現している。LC共振器だからQ値はさほど高くないが、ピーク周波数を常にモニターしておき、フィードバック回路で調整する。このクロック発生器の周波数-温度特性の変動は、±100ppm以内におさまっている。

この1チップには、LC共振器と分周器に加え、定電流回路を使った温度補償回路、周波数をデジタル的にプログラムする96ビットの不揮発性メモリー、EMIノイズの発生を抑える拡がり拡散(spread spectrum)クロック発生回路、その他インターフェース回路などを集積している。

用途はさまざまで、まずはデジタルテレビ、ディスプレイからの要求に応えるほか、マルチファンクションプリンタやコンピュータなどの用途もある。周波数は分周器の分周比率を変えるだけですむ。この製品では、ファームウエアで10〜66MHzの範囲で変える。ちなみにMM8511のパッケージは8ピンのTSSOPあるいはDFNを用意している。MM8511のサンプル出荷時期は特定ユーザー向けに5月から始め、一般ユーザー向けのサンプルは7月から始める予定である。製品単価は、1000個単位で購入する場合1.35ドル。

今後、複数のクロック周波数をプログラマブルにする、あるいはさらなる高周波にも対応する、など製品のポートフォリオを広げていく。今のところ周波数は数100kHzから数100MHzまで作り出せる。同社はチップの設計・販売に加え、大手ユーザーにはIPとしても供給していく計画である。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム