ICチップを基板に埋め込む技術が相次いで登場

プリント回路基板の中に、チップコンデンサやチップ抵抗などを埋め込んで、実装密度を上げる動きが昨年から活発になってきたが、半導体チップまで埋め込んでしまおうという動きが出てきた。インターネプコン・ジャパン2008では、WLP(ウェーハレベルパッケージ)に収めたシリコンチップを基板の中に埋め込む技術が相次いで登場した。

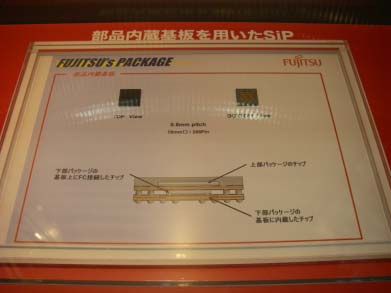

富士通は、WLPによるチップではないが、8~9mm角で300ピンのチップをプリント基板の中に埋め込み、その基板の上にフリップチップで別の半導体チップを載せた。このプリント基板は一種のIC基板となり、その大きさは18mm角、ボールピッチが0.8mm、端子数が288ピンとよくある大きさに半導体チップを収めている。このICのさらに上にPoPで、3番目のICパッケージを載せた形である(写真1)。

ルネサステクノロジは、プリント基板大手の日本シイエムケイと共同で、IC内蔵基板を開発、無線LANの評価ボートに応用してみた。このRFIC評価基板で2.4GHzでの動作を確認した。ルネサスによると、基板内蔵ICのメリットは、実装密度を上げられるという一般的な理由のほかに、シールドが容易になることからノイズを抑えることができる、としている。

試作した評価ボードは、6層配線で、チップを埋め込んだ基板全体の厚さは0.48mmしかない。ルネサスは回路設計や実装、シミュレーションなどを担当し、基板作製はシイエムケイが担当した。実用化には、コストの問題があるため、量産方法の確立と付加価値をどう高めるかという問題が残っている。

フジクラは、WLPパッケージに収めたICチップをポリイミド多層基板内に埋め込み、ビルドアップ手法によりポリイミド層を4層積層、配線層は6層形成した。260℃のJEDEC Lv.2に相当するハンダ耐熱試験で、信頼性を確認している。層間の配線には導電ペーストのビアを利用した。

基板の厚さは全体で210μmしかなく、ライン/スペースは40/40μmで、ビアピッチは300μm。この基板で光ピックアップやカメラモジュールも試作している。ICチップの厚さは100μmで、携帯電話のアプリケーションプロセッサなどに応用できるとみている。

カシオ計算機は、WLPパッケージのICを基板に埋め込むEWLP技術のエコシステムを形成できるEWLPコンソシアムを中心となって活動してきたが、今回のインターネプコンで二つの実用化例を紹介している。

一つは、トッパンNECサーキットソリューションズが採用したワンセグ用チューナモジュール(写真2)で、OFDM変調LSIチップのWLPを埋め込んでいる。チップの厚さは0.3mmで、モジュール全体の厚さは1.55mmである。6層のビルドアップ法で形成している。

もう一つは、日本シイエムケイが時計用ICにEWLPを採用した例である(写真3)。これも6層のビルドアップ基板を使い、ICを埋め込んだ。基板は0.8mmしか厚さはない。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム