Mentor Graphics、SI/PIや3D電磁界解析を含む総合シミュレータを発売

LSIの設計からPCB設計、組み込みシステムまで広くカバーしているMentor Graphicsは、プリント回路基板上を伝送線路が走るような高速信号伝送やノイズ発生をシミュレーションできる総合シミュレータツールHyperLynxを発表した。従来の伝送シミュレータと比べ、数十倍も高速に結果が得られるとしている。

図1 SI/PIや3D電磁解析ソルバ、DRCを統合したHyperLynx 出典:Mentor Graphics

HyperLynxには、シグナルインテグリティ(SI)とパワーインテグリティ(PI)、3次元電磁界(EM)ソルバといったシミュレータと、高速デザインルールチェック(DRC)などのソフトウエアが入っている。インテグリティとは、入力波形に対して、出力波形が崩れずに伝送されることが理想的であるが、その理想にどれだけ近づいているのかを分析する技術である。パルス信号をきれいな波形で送信した後、伝送線路を伝わるうちに崩れてしまうことがよくある。崩れすぎると1と0の波形を判別できなくなる(図2)。何Gbpsまで伝送できるか、という意味は、伝送した後に1と0を判別できる最大のデータレートを指している。

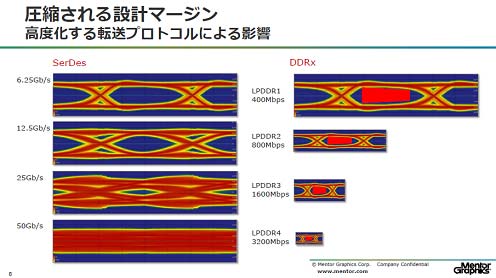

図2 1と0を判別するアイパターン (eye pattern) は高速化すればするほど、目(eye)がつぶれてきて判別できなくなる 出典:Mentor Graphics

シグナルインテグリティ(Signal integrity)は、回路の信号がきちんとしたパルス波形で忠実に伝達されているかをチェックする技術で、直訳すると信号忠実度だが、信号品質と訳されている。配線を伝わる信号は、浮遊容量や浮遊インダクタンスの影響を受け、最初に入力したパルス波形は四角形から必ず崩れる。それでも崩れる程度が少なければ、配線の終端側でパルスとして認識できる。

パワーインテグリティは、電源ラインの崩れを表す言葉であり、電源ラインが例えば5Vならどのようなことがあっても5Vから崩れていないかをチェックする。電源品質と訳されている。通常は、電源ラインのどこかで大電流が引き出されると電圧が5Vから一時的に下がるようになる。家の流し台で水道水を使っている時に、トイレなど大量の水を一気に使えば、水が細くなる現象と同じことだ。パワーインテグリティはきちんと5Vが確保されている状況を表す尺度である。

3D電磁界解析は電磁波、すなわち電波としての性質を調べるための手段であり、単なる配線が直流とは全く異なる状態になることを知ることができる。ノイズは電磁波であり、飛んで来たり発生したりしている状態を知れば、防ぐ・抑えることができるようになる。電子回路ではプリント基板であろうとシリコン半導体チップであろうと同じように、高速・高周波動作や大電流動作では、SIやPI、3D電磁界解析が必要になる。

高速ルールチェックDRCは、上のようなシミュレーションとは違い、回路パターンや配線などの設計データがデザインルールに違反していないかどうかをチェックするためのツール。回路が複雑になればもはや人の眼で違反をチェックするのが大変なほど膨大になってくるため、コンピュータを使ってルール違反を調べる。

こういったチェック機能は、これまで個別にあり、しかもそれぞれのGUIを持っていたため、使いづらく結果としてチェック時間がかかっていた。加えて、プリント回路は多ピン化が進み設計は複雑になってきた。例えば、ジェット戦闘機パイロットのヘルメット内にはフレキシブル基板上に2300点以上の部品が載り、1万2000個ものビアが開いている。電源電圧も30以上の電源レールが形成されている。こういった基板回路を試作する前に、シミュレーションを使ってSIやPI、ノイズの影響などをチェックし、十分な余裕で動作しているかどうかを確認しておく必要が高まっている。作ってから修正だと時間がかかり、さらに動作余裕に関しても調べにくい。試作前にシミュレーションで確認しておけば1回で正常に動作する可能性は高まる。

特にPCI Expressのような高速シリアルインタフェースだと配線路の終端でパルス波形が判別できないこともある(図2)。確認は必須だ。また、メモリでもDDR3からDDR4、さらにその先にはHMC(Hybrid Memory Cube)やHBM(High Bandwidth Memory)のような3次元スタックメモリでの動作確認が必要になる。

演算能力の高いプロセッサやFPGAなどでは微細化による低電圧化でビアが増加するため、その部分でのリターンパスによる影響、ボンディングワイヤ接続によるインダクタンスの増加によるSI/PIのチェックは欠かせなくなる。このために、SI/PIのシミュレーションモデルを構築することは時間がかかり、技術的にも難しい。さらに3D実装のシミュレーションも必要になる。専門的なエキスパートを数多く抱えなければ問題を解決できなくなる。

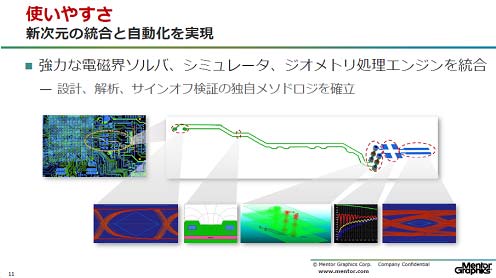

図3 LSIからの信号が終端に伝わる様子を完全シミュレートできる 出典:Mentor Graphics

HyperLynxは、高精度のシミュレーションを高速に実行できる上に、統一したGUIを使って使いやすいというメリットがある。例えば、図3のような配線では半導体チップのパッドの入り口での1、0伝送波形(アイパターン)や、途中での断面形状、多層ビアの3次元形状、キャパシタを設けた場所での波形の確認、最終端でのアイパターン、といった一連の動作や形状を知ることができる。形状はジオメトリエンジンを搭載しているから表せる。「長い配線のIRドロップや、PIのシミュレーションは従来の10~15倍速かったとある顧客から言われた」とMentor Graphics社System Design Division、Business Development ManagerのDavid Wiens氏は語る。

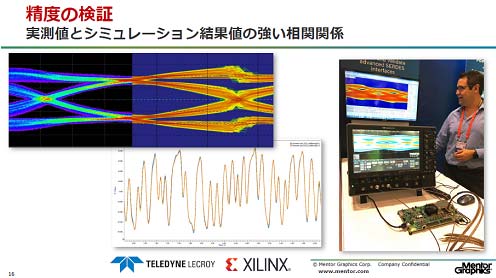

しかも精度は高い。測定器を使った実測値とシミュレーション値の相関は高く、ほとんど一致している。図4はXilinxのFPGAを使って高速伝送した時の測定値とHyperLynxシミュレータとの比較である。

図4 実測とシミュレーションはよく一致している 出典:Mentor Graphics

こういった高精度で高速化を実現できたのは、設計データと豊富なシミュレーションツールを用意し、それらを自動的に判別するからである。DRCで配線のルールをチェックし、各種回路シミュレータを持っている。SPICEやIBISに加え、3次元的な形状を作り・解析するための有限要素法(FEM)や電磁界のsパラメータモデルもある。加えて、ビアの影響やマイクロストリップラインの解析に必要な3Dの電磁界解析ツールでは、実は2.5D解析、すなわちquasi-static(準静的)なソルバを使って形状を単純化することで高速化を図っている。純粋に3次元解析だと精度は高いが計算時間がかかりすぎる。ここでは精度が必要な場所は3Dで、精度をそれほど必要としない場所は2次元で解析する。

HyperLynxの賢い所だが、伝送路に沿って信号の流れを解析していく場合、寸法や形状パターンを見て、どのシミュレーションモデルを使うべきかを自動的に判断するとしている。PCB設計データはMentorだけではなく、図研やCadence Allegroの設計データもインポートできるという。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム