3次元ICや基板内蔵ICのテスト法の主流になるか、バウンダリスキャン

バウンダリスキャン法がBGAや3次元ICのハンダボールの接続をテストする手法として、JPCA(日本電子回路工業会)ショー2013で注目された。アンドールシステムサポートが積極的にこの手法を推進しているのに加え、富士通インターコネクトテクノロジーズも、スーパーコンピュータ「京」のテストにこの手法を使っていたと述べた。

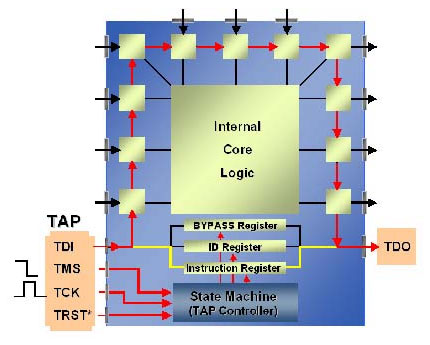

図1 バウンダリスキャン法の概略図 LSIと端子との間にロジックセルを入れ端子の接続性を調べる 出典:アンドールシステムサポート

これまで、3次元ICや多ピンBGAなどハンダボールや電極ピラーを使ったLSIチップと基板の電極パッドとの接続の様子をチェックしたくてもできなかった。TEM(透過型電子顕微鏡)でもSEM(走査型電子顕微鏡)でも電極同士が完全に接続されているかどうかを1個ずつ検査することはほぼ不可能だった。

このため物理的につながっているか、オープンになっているか、電気的にテストをするしか方法がなかった。今回、JPCAショーで注目された技術の一つが電気的に接続状態を知ることができるバウンダリスキャン法である(図1)。この方法はテスト容易化設計手法の一つとして1980年代に提案されたが、これまではあまり普及してこなかった。ただ、富士通インターコネクトは、1990年頃メインフレームコンピュータのテストから使っていたが、それ以降、富士通社内の全製品に適用してきたと述べている。

JPCAショーで注目された理由として、富士通インターコネクトは、部品内蔵プリント基板が最近使われるようになってきたためとする。LSIへの接続端子やテストパッドにプローブを充てるインサーキットテスト手法は、接続端子が見えなくなっている基板やデバイスにはもはや使えない。

図1のInternal Core Logicと書かれたものがロジックLSIである。その周りに配置された小さな四角がJTAG(Joint Test Action Group)ロジックセルである。バウンダリスキャンテスト法は別名JTAGとも言われるが、JTAGは元々、このテスト法を提案した標準化団体の名称だった。図には書かれていないがBGAのボール1個が1個のJTAGセルとつながっている。この方法では、シフトレジスタを構成するようにJTAGセルを直列接続し、それぞれのセルからの出力状態を把握できるようにしておけば、各セルと対応するBGAボールとのつながり状態を把握できる。

隣接する端子間がショートしていれば、ハンダがブリッジだったり、銀のデンドライトやウィスカーの成長によるものだったり、原因を探ることができる。またオープン不良では、ハンダが接続部で合金化されずに薄い被膜ができていた、というような事例があり、富士通インターコネクトから発表された。

図2 アンドールシステムサポートが提供するJTAGコントローラと基板、統合環境ツールProVision

アンドールシステムサポートは、4本の信号で基板全体をテストできるJTAGコントローラと、ProVisionと呼ぶ統合環境ツールを販売している(図2)。JTAGコントローラは、テスト信号を提供するためのハードウエアで、ProVisionはテストパターンを生成するための統合ソフトウエア。4本のテスト信号は、テストパターンを出力する端子と、スキャンして結果を入力する端子、クロック端子、テストモード選択端子である。オプションとしてJTAGリセット端子もある。

さらに、非テストチップを直列にデイジーチェーンのように接続し、バウンダリスキャンのテストパターンを入力すると、直列接続されたチップの接続状態をテストできる。さらに基板を複数枚接続してスキャンできるが、その場合にはScanBridgeと呼ぶシステムレベルデバイスを各基板に取り付ける必要があり、アンドールはこのデバイスも提供している。バウンダリスキャンテスト法はようやく普及しそうだ。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム