Samsung、4チップ積層TSVで128GBのDIMMを量産開始

Samsung ElectronicsがTSV(Through silicon via)を使い、DRAMチップを4枚重ねた構造のメモリパッケージを9個使った128GバイトのDDR4メモリモジュールの量産を開始した。ハイエンドの企業向けサーバーやデータセンター向けのメモリモジュール。

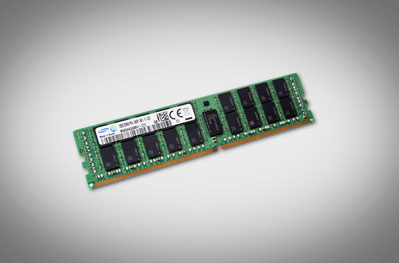

図1 Samsungが量産開始した128GB DDR4モジュール 出典:Business Wire

DRAMチップを複数枚重ねてTSV技術などで容量を増やし、メモリとCPUとの距離を短くしコンピュータシステムの速度を上げようという動きは最近特に多い。もはやプロセッサ(CPU)の速度でコンピュータシステムの性能が上がる訳ではなく、メモリ容量を上げ、CPUと大量のデータをやり取りする方がシステム速度は高まる。

製造プロセスとしては、DRAM容量をシングルチップで上げることは難しくなってきている。DRAMのキャパシタを増加させる技術が限界に近付いてきているためだ。今回使われたチップは、DRAMとして最も微細な20nmルールで製造され、チップ単体の容量は8Gビット(=1Gバイト)である。一つのモールドパッケージにはチップを4枚重ねているため、1パッケージ当たり4Gバイトの容量となる。このメモリモジュールRDIMM(Registered Dual In-line Memory Module)は両面実装しており、全部で36個のメモリパッケージを搭載している。物理的には、全部で144Gバイトを積んでいる形になる。このモジュールでは1ビットを誤り訂正のためのパリティビットとしているため、事実上は8ビット+1ビットの9ビットを1バイトと数えている。だから実際に使える実効メモリ容量は128Gバイトとなる。

Samsungは2014年に最初のTSVスタックで64GバイトのDDR4 DRAM RDIMMを開発していた。今回のRDIMMは容量をさらに2倍に増やした。

従来のDRAMは、ワイヤーボンディングによって、DRAMチップを重ねていたが、チップを互い違いに積み重ねざるを得なかった。ボンディングパッド部分がチップの縁に配置されてあったためだ。これでは、チップ間の配線の距離が長くなり、データ幅を広げると配線の遅延やスキュー、レーシングなどの問題が発生しやすくなり、誤動作につながった。このためバンド幅の拡大には限界があった。

今回のようにTSVを用いれば、1枚のシリコンチップの厚さは数十µmと薄いため、チップ間の配線長も数十µmと短縮できる。さらに、今回は、1パッケージに4枚の重ねたチップの内の一つをマスターチップとして、データバッファ機能を持たせた。このことによって、性能と消費電力を最適化できた。この結果、今回のメモリモジュールでは最高2.4 Gbpsと従来の64GバイトLR(Load reduced)DIMM品(4枚スタックだがワイヤーボンディング使用)よりも2倍の性能が得られると同時に、消費電力は半減した。

同社はTSVの生産を加速し、20nm 8GビットDRAMチップの量産立ち上げを速めることで、DRAMの超大容量化に応えていく。さらに新しいTSV技術を使ったDRAMモジュールを拡張し、128GバイトのLR DIMMなどのモジュールも数週間以内に揃えていく計画だ。今後、TSVによるDRAMモジュールの更なる高速化にも対応していくとして、最大2,667Mbps、および3,200Mbpsといったデータ転送速度のモジュールも展開し、HBM(High Bandwidth Memory)などの製品へも広げていくとしている。

参考資料

1. Samsung Starts Mass Producing Industry’s First 128-Gigabyte DDR4 Modules for Enterprise Servers, Business Wire (2015/11/25)

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム