メンター、65nm以下のCMPの配線バラつきを低減する設計ツールCalibreを強化

メンター・グラフィックスは、配線層のバラつきによってタイミングの変動が大きくなってくる65nm以下のプロセスにおいて、プロセス上でバラつきを減らすのではなく設計上からプロセスばらつきを減らすための設計ツールCalibre platformの機能を強化し、その詳細を明らかにした。45nm、32nmと微細化が進むにつれ、CMP(chemical mechanical polishing)による配線の幅や間隔などの加工バラつきはもはや許容範囲に収まらなくなってくる。この製品は加工バラつきを設計上から減らそうという訳だ。

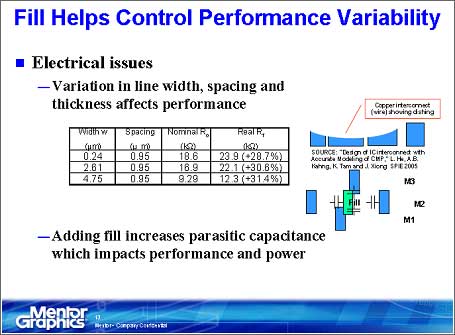

LSIの多層配線技術では、CMPを使って平坦化を図るが、Cu配線の間隔が広い場所と狭い場所で、削られる量が変わり、配線が太いとディッシングと呼ばれる過剰な削減が見られる。このため、ダミーフィルと呼ばれるCu配線を隙間に入れておき、配線密度をほぼ一定にしておこうという方法を採用してきた。しかも挿入し忘れたために配線厚のバラつきが増加することを嫌うため、やたらとダミーフィルを配置してきた。しかし、この方法では、本来の信号用Cu配線とダミーフィル配線との間にキャパシタンスが発生し、高速動作やシグナルインテグリティに影響を及ぼす。設計通りのタイミングが得られない恐れも出てくる。

90nm程度くらいまでなら何とか従来のダミーフィルでも対処できた。しかし、65nm以下と微細化するにつれ、配線の厚さのバラつきは大きくなる。配線が微細になるにつれ、長さ、幅、厚さともほぼ同じような割合で縮小していかなければならないためである。厚さのバラつきは±10nm以下であるため、65nmプロセスでは9%のばらつきが45nmでは14%に増え、32nmノードでは20%にも達してしまう。厚さがこれだけバラつくと配線抵抗もバラつく。こうなると設計通りのタイミングを満足できなくなる恐れがある。設計し直さなければならなくなる。できるだけバラつきを減らしたい。

そこで、メンターが開発したこのCalibre platformに3つの技術を導入し、これからの問題に対処した。まず一つはSmartFill。これは空いている所にやたらと入れるのではなく、タイミングといった性能に関係する所にだけ配置するという技術である。配線密度や配線パターンの周囲長などによって入れ方や入れる場所を変えるという「賢い(smart)」方法だ。

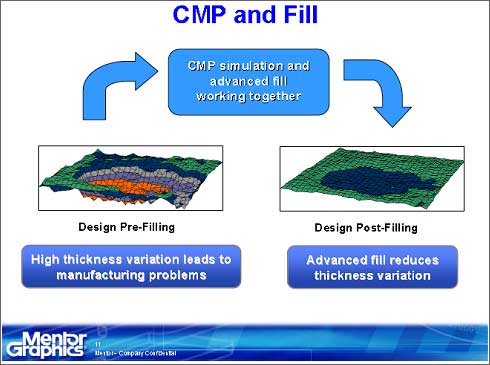

二つ目は、配線厚のバラつき分布を視覚化し、最も多くの量を削られた「ホットスポット」を検出する。これにはCalibre CMPシミュレータ、あるいはファウンドリが創るモデルに基づいたシミュレータを利用する。このCMPモデルでは、まずCuを削る前の埋め込まれた状態の2次元分布、ある時間削った時の分布、さらに削ったときの分布、最終的な分布を2次元のカラー分布で表わすことで最も薄く削りすぎたような場所を検出する。

この後、配線の厚さ分布に基づいてタイミングや電気特性のシミュレータにかけ、問題がないかどうかをチェックする。そして、問題がありそうな場所の密度と厚さに基づき、モデルベースで計算したフィルを追加してみる。これを繰り返し、問題ないタイミングと電気特性が得られたら、それを最終の配線パターンとする。

半導体メーカーやファウンドリは各社各様のプロセスを使っているため、「プロセスモデルは各社で作ってもらうことにしている」、と同社プロダクトマーケティングマネジャーのJeff Wilson氏は言う。それも配線層ごとに各社内部でも違うことが多いという。同じCMPマシンを使うとしても、チューニングしたり、たとえしていなくてもスラリーの粒径が異なるとか、メッキ条件が違うとか、プロセス条件は違うため、モデル作成を各社にお願いするというわけだ。大手企業の中には、90nmを条件通りに生産開始しても量産中にCMPの条件をチューニングして変えていくこともあるという。モデルは常にアップデートしたものにしなければ新製品の1発完動できない。

メンターはこのツールにより、バーチャルCMPモデルを提供していることになる。このCalibre DFMプラットフォームを使って、英国のファブレスCSR社が設計した65nmデバイスは1発完動したとWilson氏はいう。この場合は、CalibreをファウンドリであるTSMCが使って配線厚のDFM補正しタイミングシミュレーションを駆使し、最終マスクデータをTSMCが起こした。CSR社は物理設計にまでは関与しないため、RTLデータをTSMCに手渡し、スペックを満たしていることを確認するだけ。GDS IIフォーマットのマスクデータはメンターのツールを使ってTSMCが作成する。

日本のIDMに対しては、自社でモデルを作り、メンターのCalibreを使ってこれまではダミーフィルを作ってきた。この新製品で、これからのLSIにはCMP-awareなダミーパターンを作るのに最適とメンター・グラフィックス・ジャパンのテクニカル・セールス本部長の青木淳一氏はいう。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム