特集:英国株式会社 (4)マルチコアDSPで無線インフラ市場へ

今から2000年ほど前、ローマ人が支配していたイギリス南西部の街バース(Bath)は、温泉が湧きお風呂の語源にもなった街である。ここに世界の半導体メーカーやシステムメーカーを相手にする、若い半導体ファブレス企業がある。創立7年のpicoChip Designs社の経営陣はグローバルな企業からやってきた人たちが圧倒的に多い。Oak Technology、IBM Microelectronics、Cadence Design Systems、Conexant Systems、Agere Systems、Vodafone、Analog Devicesなど世界各地の企業から集まっている。

picoChip社が得意とする製品は、ワイヤレス分野に特化したマルチコアDSPプロセッサだ。「使いやすく、コスト・パフォーマンスがよく低消費電力であり、mWあたりのMIPS性能は従来のDSP製品と比べて10〜40倍優れている」と同社マーケティング担当副社長のRupert Baines氏はいう。同氏は欧州大陸のAtlantic Telecom、その前は米Analog Devicesにもいた。

狙う市場は、セルラー電話の3G以降のHSDPA、HSUPA、LTE、フェムトセルなどのセルラーネットワークに加え、WiMAXネットワークなど新しい高速ネットワークの基地局向けチップである。特に、最近注目されているフェムトセル向けにはこれまでのような高価なDSPは使えない。フェムトセルは家庭やオフィスで使う小さな基地局だからである。せいぜい家庭用ルーター程度の価格に納めなければならない。

実は、Baines氏が述べたこの数字は第三者の評価機関であるBDTI(バークレイ・デザイン・テクノロジー社)がベンチマークテストしたもので、picoChip社の最初の製品PC102と、Texas Instruments社のハイエンドDSP製品TMS320C6455を1GHzで動作させ、Freescale SemiconductorのDSP MPC8144を1GHzで動作させて比較したもの。PC102は160MHzで動作させた。絶対的な性能も、ベンチマーク・チャンネル数、チャンネル当たりのコストなどで比較している。ニュースリリースが出ている(http://www.picochip.com/press/press_releases/press099)。

picoChipは単なるファブレスの半導体企業ではない。チップ開発に必要なレファレンスデザインボードや、3G/WiMAX、LTEすべてをカバーするソリューションまでも提供する。半導体チップそのものの性能が良いだけではない。ソフトウエア無線方式であるため、ベースバンド設計をソフトウエアだけで変更できる。だから、3GやLTEになろうが、WiMAXになろうが関係なくどちらにでも対応できる。

DSPチップとしては、高性能・低価格・フレキシビリティと三拍子備えた半導体である。同社はまだベンチャーといえるような小さな企業で、バースに本社を置き、全従業員は130名程度だ。ここに90数名ほど集い、30名程度が世界各地のセールスオフィス(北京、東京、ボストン、ソウル、サンジェゴなど)にいる。ベンチャーキャピタルから4回に渡る融資を受けてきた。技術アドバイザリボードには、XMOS Semiconductor社の創立者でもあるDavid Mayブリストル大学教授(英国特集(2)を参照:)も名を連ねている。

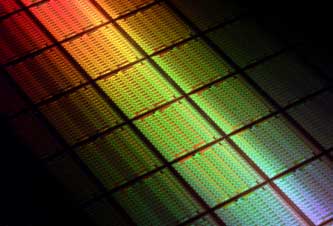

130nmルールで作った最初のチップPC102は2004年に10~20万個生産し、今は90nmの第2世代チップは2006年に発売した。累計で100万個にも達するという。今年発売するチップは65nmルールで作るPC20x、PC302/305を予定している。品種をいくつか設けているのは、大きな基地局からフェムトセルまで広くカバーするためである。

picoChip社のマルチコアDSPチップは1チップ上に16ビットのDSPコアを数百個並列に並べた構造をもつ。マルチコアにした理由は、シングルコアで性能を上げる場合にトランジスタ数、すなわちチップ面積が増加してしまうためだ。2007年にIntel社が分析調査した結果、MIPS数で性能を2倍に上げるのならトランジスタ面積は3倍に増え、4倍に上げれば9倍にも増えてしまうことがわかった。

picoChip社は、理想的なDSPを分析し、何トランジスタで何MIPSのDSPが1個のDSPコアとしてベストなのかを検討した。その結果、16ビットのDSPコアで100〜200MHzで動作させた、3ウエイVLIWアーキテクチャが最適だと見出した。このコアを最小のビルディングブロック単位として、300個程度並列動作するマルチコアDSPを設計した。最初のチップであるPC102(130nmプロセス)では、308個のDSPコアを集積した。このチップの性能は、クロック周波数160MHzで、197GIPS(giga instructions per second)、積和演算速度は38.6GMACs、メモリーの転送速度は3.3Tビット/秒と極めて高い性能を示した。ただし、第一世代製品のPC102の消費電力は5Wとやや大きい。

性能はDSPコアの数に比例するが、面積もその分大きくなる。このPC102を4個並べDSPを1200個のコアに並列動作させると、800GIPSになるとしている。最も大きな規模の商用システムは4800個のDSPコアで3.3TIPSという性能を示した。ちなみに現在出荷中のPC202は90nmプロセスで製造しており、20〜30ドル程度の価格だという。

同じ機能をFPGAで実現しようとすると、面積効率は悪い。FPGAや従来のDSPと比較するとシリコン面積当たりの性能(演算数/mm2)は専用のASICよりは悪いものの、プログラマブルデバイスの中では最も良い位置にいる。

各種の無線方式に対してはソフトウエアで切り替えられる、ソフトウエア無線である。ソフトウエアは従来のDSPのプログラムと同様、C言語あるいはアセンブラ言語で書ける。プログラムをブロックダイヤグラムと結びつけることができる。デジタルLSIで最近よく見かけるCADとCAEを結びつけ、LSIの性能を評価できるようにしているようなものだという。

picoChip社はファブレス半導体が主なビジネスではあるが、ソフトウエアおよびハードウエア開発ツールも提供している。W-CDMAやHSDPA、LTE、CDMA2000/EVDO、WiMAXなどの各種の通信方式に対してはソフトウエアで対処するため、ソフトウエアリファレンスデザインを使い、チップの上のインタフェースやハードウエアの変更に対してはハードウエアプラットフォームを使う。それぞれ10種類を超えるツールがある。各ツールは最小の機能を載せてあり、これだけでもシステムは組める。すなわちソリューションとなっている。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム