TSMCの先端パッケージ工場を日本へ誘致するワケとは?

TSMCが経済産業省と話し合いを持ち、日本に先端ICパッケージ技術の工場設立を検討するというニュースが流れた。どうやらこのニュースは事実のようだ。日本経済新聞は、1月5日に現地報道という形で伝えた。確かにTSMCはCoWoSやInFOと呼ぶ2.5D/3D-ICパッケージ技術を手掛けており、OSATのお株を奪う勢いであることは事実だ。

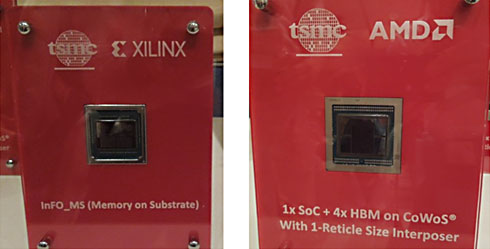

図1 TSMCが持つInFOやCoWoS技術で実装したチップ 筆者撮影

日本における新工場は東京に設立すると現地では報じられているが、東京のどこになるのか場所については触れていない。これまで明らかになっていることは、経済産業省と折半で日本に合弁会社を設立すること、前工程ではなく後工程の工場であること。

経産省は昨年、前工程の誘致をTSMCに持ちかけていたが、見事に断られた。同省は今年度はそのための予算をすでに計上しており、TSMCの半導体工場を何が何でも誘致するため、前工程のファウンドリではなく、後工程の工場を設立しようということのようだ。とにかくTSMCの半導体工場を日本に持ってこれたとなれば経産省のメンツは保持され、TSMCの半導体工場を日本に持ってきたという実績が残ることになる。

では、TSMCはなぜこの話に乗ったのか。この話にはさまざまな事実を積み上げる必要がある。一つは、TSMCが米国アリゾナ州に5nmプロセスの最新鋭工場を設立することを決め(参考資料1)、35億ドルという資本金まで取締役会で決定したことだ(参考資料2)。このため、日本に前工程の工場を作るという選択は消えた。

TSMCは台湾北部の新竹の本社工場だけではなく、台中、台南など、地震やテロなどのリスクに備えて事業継続のため各地に工場を分散させている。台湾以外でも中国の南京とシンガポールにも工場を稼働させている。米国ワシントン州にも工場を持っているが、200mmウェーハファブであり、昨年のアリゾナ工場ほどの規模ではない。今回、日本に誘致することで後工程工場のリスク分散ということになりそうだ。

もう一つは東京大学の持つ最先端MOSトランジスタ技術である。2019年にTSMCと東大d.labは提携を結び(参考資料3)、東大で7nmや5nmのLSI設計を行い、その製造をTSMCに依頼できるようになった。東大側としても最先端プロセスでLSIを設計したいという思惑がある。TSMCとしては今後の5nm、3nmへと微細化が続く上でプロセスを設計するために東大のMOSトランジスタ技術が欲しかった。東大には量子力学のトンネル効果を利用したTFET技術や化合物半導体とのヘテロ技術もある。TSMC1社だけで3nmあるいは2nmプロセスを開発するよりは大学の知恵を借りる方が開発費は安く済む。Samsungのファウンドリビジネスの追い上げもある。

それだけではない。TSMCはこれまで、Appleやファーウェイ、QualcommをはじめとするスマートフォンビジネスやAMDのCPUビジネスを中心にファウンドリサービスを行ってきた。今後は、自動運転や電動化をはじめとするクルマ事業の成長分野にも進出できる。この産業は日本がドイツと並んで強いことをTSMCは理解している。さらに日本は産業用ロボットやPLC(Programmable Logic Controller)、産業機器でも世界をリードしている。これからは再生エネルギー制御機器にも成長機会が増える。実は日本が得意な分野にこういった未来のテクノロジーがたくさんある、と海外の目には映っている。日本法人に力を入れる外資系企業には、こういった日本の技術に目を向けている所が多い。

TSMCは日本にデザインセンターを開設するための人材募集を積極的に行っている。RTLからGDSまでの設計やメモリコンパイラのエンジニア、レイアウトエンジニア、IP開発者、特性評価エンジニア、論理合成/高位合成エンジニアなどを求めている。ファウンドリビジネスで重要なことは、設計専門のデザインセンターを持つことだ。さもなければ顧客は来ないからだ。自前の半導体を欲しいIT企業は多い。しかしLSI設計は難しい上に他に応用が利かないから積極的にやりたくない。プログラミングからRTL出力、プログラム検証、論理合成、ネットリスト出力、レイアウト、配置配線、そしてマスク出力、という設計工程を一から学ぶ暇があるなら、AIのアルゴリズムや新しいソフトウエアの開発をしていたい。だからこそ、LSI設計専門のデザインハウスが欠かせないのである。日本でファウンドリと称している製造工場は、設計能力がないにもかかわらずデザインハウスと手を組んでいないため、いつまでたっても顧客はこない。

これからのLSI、特にSoCは、CPUとGPUやDSP、ISPなどヘテロプロセッサとの集積と、Siに化合物半導体を集積する技術が重要になる(参考資料4)。ヘテロプロセッサはRISC-Vで命令セットを統一する動きを利用するとして(参考資料5)、Siと化合物半導体のとのヘテロ集積技術は、実は日本がまだ強い。

2次元平面上にトランジスタを多く集積するムーアの法則は行き詰ってきたため、5nmから3nm、2nmへの微細化は進める一方で、無理なく製造するためのチップレット(小さいチップやIPをチップ化したもの)をSiインターポーザなどに集積する動きも見逃せない。先端パッケージ技術は、Intelが始めたチップレット実装(参考資料6)もその一つである。ここに2.5Dや3DのICも集積する。

TSMCはコスト的に折り合いを付けながら3次元実装を目指す技術、InFO(Integrated Fan-Out)やCoWoS(Chip-on-Wafer-on-Substrate)技術に力を入れてきた。この先端パッケージはWLP(ウェーハレベルパッケージ)や実装したパッケージがチップと同程度かやや大きい程度の超小型パッケージである。最近では3次元実装のSoIC技術(図2)も開発している。

図2 TSMCの3次元ICであるTSMC-SoIC技術 出典:TSMC

ウェーハをチップにカットする前にウェーハへのバンプ形成やモールディングなどで加工するため、前工程製造請負のTSMCが手掛けているが、OSATトップの台湾ASEも同様な先端パッケージを手掛けている。つまり競争が激しくなりつつある。

さらに、日本には新光電気工業やイビデンなどの先端パッケージ技術を扱う会社がある。単なる後工程のOSATではない。加えて、後工程の製造装置産業では、ウェーハの切断を行うディスコや東京精密工業、モールディングのアピックヤマダとボンダーの新川を傘下に治めたヤマハ発動機の子会社ヤマハモーターロボティクスホールディングス、モールディングに強いTOWAなどの装置メーカーもある。TSMCにとっては装置産業へのサプライチェーンを利用しやすくなるというメリットもある。

日本に誘致する先端パッケージ工場は、こういったInFOやCoWoS技術、3D-ICを使う工場となるだろう。今や後工程=遅れた技術、という図式は成り立たなくなりつつある。

参考資料

1. TSMCの米国先端工場設立の背景に華為つぶし (2020/05/18)

2. AppleがMacのCPUをIntelから独自に変えたのはスケーラビリティ (2020/11/16)

3. 東大とTSMCが包括提携、3nm以下のLSI実現に向けた国際協力へ (2019/11/28)

4. ISSMでヘテロ半導体技術の方向を示唆した世界の論客Nicky Lu氏 (2020/12/18)

5. 半導体プロセッサメーカーが集結した師走(IoT/セキュリティ編) (2017/12/22)

6. VLSI Sympo報告:IntelのMayberry CTO、コンピュータトレンドを語る (2020/06/19)

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム