## ID BA-P-32

## Litho APC Optimizer – Dongsub Choi

David Tien

Dongsub.choi@kla-tencor.com David.Tien@kla-tencor.com

KLA-Tencor

7<sup>th</sup> Fl., Starplaza Bldg., 92-7 Bansong-Dong, Hwaseong city, Gyeonggi Prov., 445-160 South Korea Phone: +82 -10-6778-4967 Fax: +82-31-728-9299

## Start writing your paper here.

Overlay continues to be one of the key challenges for lithography in semiconductor manufacturing, especially in light of the accelerated pace of device node shrinks. In the case of the 20nm node where 4nm overlay control will be required, we can generally group sources of overlay error into four broad categories: scanner, reticle, process, and metrology. From each of these error sources, we can further classify the type of error into residuals. remaining correctables, and wafer to wafer variability. Classifying each error in this context allows us to build a framework around better understanding how to improve overlay control based on the current status quo. For instance, the term remaining correctables as defined in this paper is a correctable error that remains even after standard corrections were applied using APC in production. Through this framework, users of the methodology discussed in this paper can better drill down and identify not only the root cause of the error but how much of the error can be further corrected using the suggested APC Optimization techniques.

In summary, this paper will describe a 3-step methodology and techniques for APC optimization, collectively referred to as Litho APC Optimizer (\*). The first step requires developing an APC Index in order to benchmark the current APC performance across different processes and devices running in the fab. The second step is to develop detection algorithms to identify in detail the areas (product/layer/equipment set) where poor APC performance can be improved. And the third step is root cause analysis and how to improve performance. Furthermore, this paper will also highlight some special considerations when using the Litho APC Optimizer for high order control which is critical for meeting the 2x node overlay control requirements associated with DPL processing.

(\*) Patent Pending

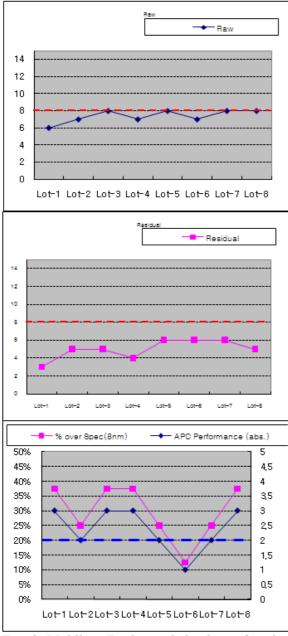

Top & Middle : Traditional display : Overlay Performance SPC chart Bottom : APC Performance SPC chart

Attach supporting data, charts and graphs, photos, or drawing in this second page