AIの積和演算に小さなDSPを数百個並べたIPコアが続々登場

ディープラーニングのニューラルネットワーク行列演算に超並列DSP回路を利用するIPがCEVAに続き、Flex Logixからも出てきた。エッジAIチップに集積するためのIPコアである。ニューラルネットの演算では8ビットや16ビットのように小さな積和演算(MAC)が適しているため、小さなDSPを大量に集積している。

ニューラルネットワークでは、基本的に1個のニューロンに積和演算(データ×重み)が多数ぶら下がる多入力1出力のパーセプトロンをモデルにしている。ただし、出力が1つでも多数のニューロンにデータを伝達していくため、電子回路のファンアウト出力が出ているようなモデルを使っている。このため、AIチップやIP回路では、積和演算(MAC: Multiply Accumulation)を多数並べた構造をしている。元々GPU(グラフィックスプロセッサ)にはMACが集積されており、しかも超並列と言えるほど小さなGPUコアが集積されているため、NvidiaのGPUがニューラルネットワークの演算によく使われている。

しかし、MACを集積している点ではDSPも同じだ。DSPは積和演算専用のマイクロプロセッサだからである。ただし、これまでのDSPは、演算精度を重視するため、32ビットを基本の単精度として64ビットの倍精度などの精密な演算に向けられていた。DSPは、FFT(高速フーリエ変換)などのような通信モデム演算に向いていた。しかし、AIニューラルネットワークに使うニューロンモデルでは、高精度よりも小さなMACを非常に多数並べる方が向いている。このため、8×16ビットとか7×7ビットのような小さなDSPをニューロンの数だけ大量に集積している。

もともとDSPコアをセールスポイントとしてきたIPベンダーのCEVAは、最近AI向きの小規模・大量のDSP回路を並べたIPコアを先行してリリースしてきた。自動運転車など画像認識のような応用では、汎用のDSPというよりは画像・映像用のDSPコアとしてCEVA-XM4製品や、さらに映像と汎用ディープラーニング用のDSPコアとしてCEVA-XM6製品がある。6月には、ドローンやロボット向けのAI SoCを設計している中国のファブレス半導体メーカーArtosyn Microelectronicsにライセンス供与したと発表している。

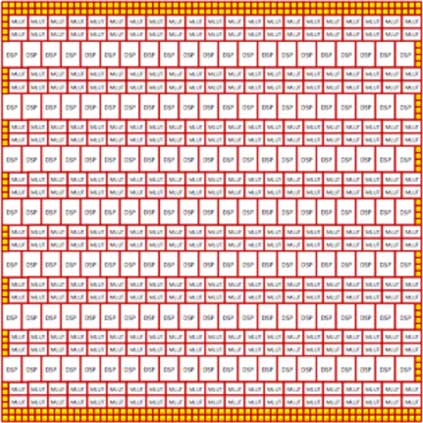

図1 Flex LogixのAI用IPコアEFLX4K AIシリーズには数百個の小さなDSPを集積 出典:Flex Logix Technologies社

これに対しFlex Logix Technologies社がリリースしたAI用IPコア(EFLX4K AIシリーズ)は、数百個のDSPコアと制御回路を集積しており、ニューラルネットワーク演算専用の回路となっている。CEVAのようなDSPコアを主力としてきた企業と違い、Flex Logixは組み込みFPGA(eFPGAと呼ぶ)を主力としてきた。そのアーキテクチャは、多数のDSPコア+FPGAのIPコアとなっている。

AIのアルゴリズムでは、今は画像や映像認識や音声認識のようなパターン認識に注目が集まっているため、畳み込みニューラルネットワークに適したMAC回路が多用されてきた。しかし、ディープラーニングのニューラルネットワークは人間の大脳皮質をモデル化したもので、大脳皮質は視覚や聴覚、行動制御、言語認識などをつかさどる組織と言われている。脳はそれ以外にもストーリー性のあるエピソードを記憶している海馬や、手足や身体の運動を精緻に制御する小脳など他の組織も多い。今後、脳をどのようにモデル化するかによって、ニューラルネットワークのモデルだけが適しているとは限らない。どのようなモデルにも専用回路で表現できるデバイスがFPGAであるから、アルゴリズムやその制御を回路で表現するFPGAを残したうえで超並列のDSPを集積したデバイスは今後も生き残る可能性は高い。

今回Flex Logixがライセンス可能なIPコアとしてリリースしたEFLX4K AI eFPGAコア製品は、8ビットのMACや16ビットMACを自由に構成可能になっており、例えば16×8ビットなども可能である。EFLX4K AIコアは16nmプロセスなら441個の8ビットMACを持つ1.2平方mmのコアとなり、1GHzで動作する。MAC演算のスピードは、ワーストケースで441 GMAC/秒のスループットを持つ。7×7ビット構成にすると22 TMAC/秒という性能が得られるとみている。IPコア内の配線には同社のXFLX配線技術を使って面積効率が高く、かつ再構成可能な回路を構成できるという。

このIPコアを使ってSoCを設計する場合には、EFLX Compilerが使え、既存のソフトウエアフローがサポートしている。このコアは6〜8ヵ月あればどのようなプロセスへもインプリメントできるという。Flex Logixは元東芝のエンジニアだった古山透氏が日本法人の社長を務める会社。

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム