TSMCのテクノロジーロードマップ(1)

TSMCがテクノロジーロードマップを2月のISSCC(International Solid-State Circuits Conference)で発表、詳細な内容をSemiconductor Digest誌が掲載している。Pete Singer編集長の許可を得て、ここに掲載する。講演したのはTSMC会長のMark Liu氏である。記事はやや長いため、前半と後半(参考資料1)に分ける。

筆者: Pete Singer、Semiconductor Digest編集長

半導体メーカーは、これまでのトランジスタレベルやチップレベルのメリットだけではなく、システムレベルでのメリットを計測する手法を採用する必要がある、とLiu氏は述べた。半導体技術は、トランジスタ技術の改良やメモリの進展、効率的な信号や電源の供給、新材料の開発やDTCO(設計とプロセスの協調最適化)、3次元構造へと発展し、ドメインスペシフィックな技術に切り分け、チップレット技術や先端パッケージング技術と結びつくのにつれ、もっと大きな価値をユーザーに提供できるようになる。

「基盤技術としての半導体産業の役割は、かつてないほど重要になっている。テクノロジーはこれまでの数十年間に渡り、私たちの社会や生活に重要な変化を及ぼしてきた。世界の人口の半分以上がオンラインでつながり、36億人のSNSや26.3億人のストリーミングビデオを楽しめるようになっている。こういった生活を変えたテクノロジー進展の中心は明らかに半導体技術である。ほとんどのイノベーションは最先端ノードに導入されたが、これは先端ノード技術が最も高速で高いエネルギー効率を生み出したからだ」とLiu氏は語る。

しかも、最先端のプロセスノードの技術がこれまでになく大きな広がりを見せている。かつてはCPUやFPGAなどが先端デバイスを構成し用途が限られていたが、7nmノードが半導体の歴史の中で分岐点となり、7nmプロセスの応用製品は、マイクロプロセッサだけではなく5GやGPU、ネットワーキング、ゲーム、自動車へと広がっている。Liuは、「TSMCの7nm技術を使った製品は150種類を超え、2020年8月時点ですでに10億個のチップを出荷したことになる。まさにテクノロジーの民主化といえる」と言う。

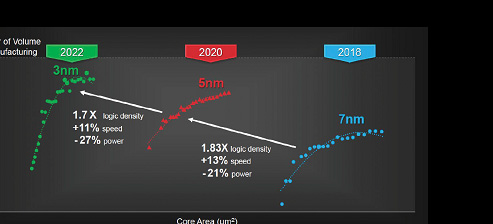

Liu氏は、テクノロジーが飽和してきたという見方を否定し、確実に5nm、3nmへと微細化は進んでいると言い「3nmプロセス開発は順調で、スケジュール通りに進んでいる」(図1)と述べている。

図1 先端テクノロジーノードは7nmから5nm、3nmへと続く 出典:TSMC, Semiconductor Digest

この先は、大学と密接に協力し、新トランジスタ構造や新材料、新アーキテクチャ、3次元集積を開発し3nm以降のノードに活かすことをTSMCは狙っている。

最先端の7nmと5nmのプロセスでは、次のような技術を採り入れた。

・ゲート絶縁膜の等価容量膜厚やトランジスタのフィン幅と形状

・駆動電流を上げるための高移動度チャンネル

・材料とプロセスの集積;前~中工程では寄生容量、寄生抵抗を下げる、

・プロセス後工程(BEOL)では、バリヤ・配線の改善、低k誘電率材料、Cuリフロー、ビアなどで抵抗や容量を下げる

・しきい電圧の不整合を最小にするための厳しいプロセス制御

・ゲートスタック構造の改善;多しきい電圧(最大7個)で回路レベルの電力・性能を最適化

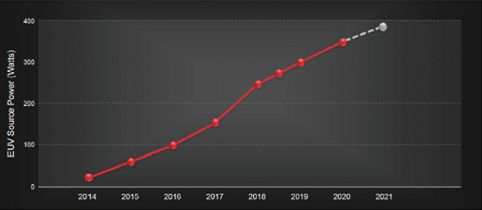

さらにEUVリソグラフィは、ArFリソグラフィの解像度のボトルネックを解消した重要なイノベーションである、とLiu氏は述べている。EUVはパターンの忠実度が高く、サイクル時間が短い。プロセスの複雑さと欠陥密度を減らした。EUVによって、5nmノードではマスク数を10枚以上減らしたという。特に配線の切断や、コンタクト、ビア、メタルのパターニングに有効だったとしている。ArFリソのマルチパターニングに対してEUVは1回のパターニングで済んだためだ。EUV光源の進歩も大きく(図2)、今や350Wに達しており、5nmの量産を実現し、3nm、2nmの開発にも道を開いたと述べている。

図2 EUV光源の進展 出典:TSMC、Semiconductor Digest

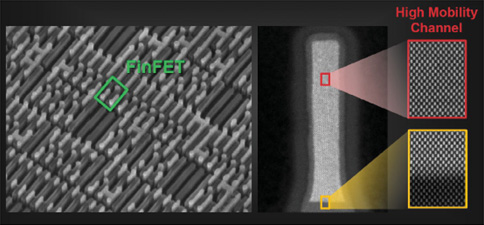

トランジスタ構造と新材料にも言及しており、従来のDennardのスケーリング則とは違い、ロジック技術がいろいろな材料とデバイスの革新、回路設計の協調最適化を利用するようになった。図3には量産にある高移動度チャンネルを特長とする5nm FinFETトランジスタを示している。

図3 高移動度チャンネルを持つFinFET 出典:TSMC、Semiconductor Digest

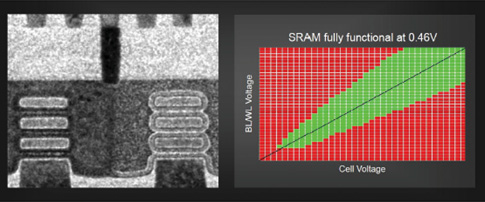

図4 FinFETを超えてナノシートトランジスタへ 出典:TSMC、Semiconductor Digest

この先のFin FETを超えるトランジスタ構造では、ナノシートトランジスタが性能と電力効率を改善するかもしれない。図4の左側がナノシートトランジスタのTEM断面写真である。シート間の密な間隔で寄生容量を減らしているという。このナノシートを使うことでドレイン電圧によって生じるバリヤ低下(drain induces barrier lowering)を防ぎ、サブスレッショルド電流の傾きを改善する。この結果、前の世代のトランジスタよりも優れた回路性能をもたらすようになる。「トランジスタ性能が上がるということはSRAM動作のVDDを下げられることを意味する」とLiu氏は語った。

参考資料

1. TSMCのテクノロジーロードマップ(2) (2021/05/21)

インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ インサイダーズ

インサイダーズ セミコンポータル編集長

セミコンポータル編集長 半導体関連市場の動向

半導体関連市場の動向 技術コンテンツ

技術コンテンツ 経営・戦略ビジョン

経営・戦略ビジョン トピックス解析コラム

トピックス解析コラム