## Improving Root Cause Analysis Accuracy Using Advanced Sensor Trace Analytics

KK Gan / Tom Ho / Joe Lee

kkgan@bistel.com / tomho@bistel.com / joelee@bistel.com BISTel America 3151 Jay Street, Suite 201, Santa Clara, CA 95054, USA Phone: +1 -408-855-8212 Fax: +1-408-855-8213

## I. MOTIVATION

Wafer yield loss directly impacts a manufacturer's revenue; therefore, it is extremely critical for engineers to find the root cause of a yield-impact issue and remedy the situation as quickly as possible. Unfortunately, wafer defect signals do not always provide a clear indicator for engineers to easily identify the root cause. The traditional, and often manual, root cause analysis process could be very time consuming and requires resources with deep domain knowledge of the process. The lengthy time-to-root-cause-identification does not only prolong production of poor-quality products, it increases manufacturing costs and limits productivity.

This presentation, through a case study, illustrates how advanced trace analytics can accurately pinpoint root causes of yield impacting issues, while greatly simplifying the root cause analysis process.

## II. WAFER LOW YIELD CASE STUDY

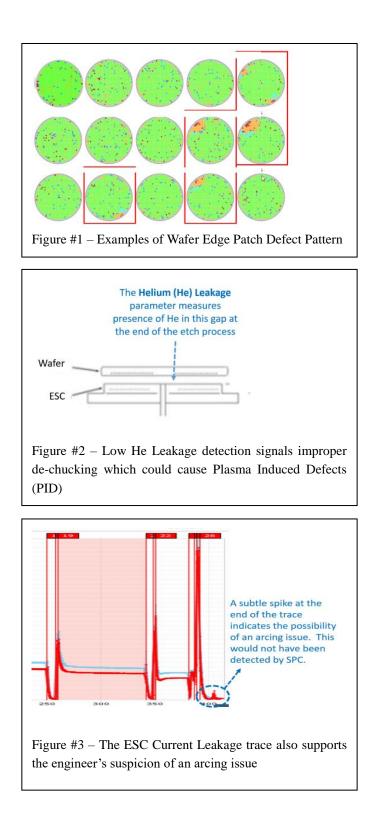

In the highlighted case study, over 30% of the wafers from two production lots suffered from wafer edge low yield patches at the 5 and 11 o'clock positions. Yield loss was up to 11% on each affected wafer (see Figure #1).

Chamber commonality was performed using the analytic tool from the existing YMS system which suggested that the issue was isolated to a specific Etch process step in a specific chamber. Correlation analysis followed using the available inline quality data (Defect Inspection, Metrology, and Electrical Test), however, no noteworthy results were found. At the same time, through domain experience, the engineer recognized this issue to be similar to a past issue related to a defective Electrostatic Chuck (ESC). He suspected that an arcing issue could potentially be causing improper de-chucking of wafers resulting in defects on the edge of the affected wafers. To confirm his suspicion, more in-depth root cause analysis would be required. This could be a long and challenging process if done manually.

To expedite the in-depth root cause analysis process, a trace analytic (TA) solution was introduced to the problem. Within minutes, the TA solution identified and ranked all potential root cause candidates at parameter level. In examining the top candidates, the engineer quickly identified that the Helium (He) Leakage parameter to be the root cause of the problem. This parameter measures the level of Helium that is present between the wafer and the ESC platform at the end of the etch process. He noticed that the measurements of this specific parameter from the low yield wafers were consistently lower than those from the high yield wafers. This indicates that the wafers were not properly decoupled from the ESC platform at the end of the process which likely resulted in Plasma Induced Defects (see Figure #2). This confirms the engineer's initial suspicion of an arcing issue.

In addition, upon further examination of the rest of the parameter candidates, the engineer discovered another parameter (an unmonitored parameter by FDC) which correlated strongly with this issue. This parameter specifically measures the ESC Current Leakage, and all the traces from the affected wafers showed a subtle spike at the end of the trace which indicates abnormalities at the end of the etch process. In normal operation, this signal should be at zero at the end of the etch process. This subtle spike further supported the arcing suspicion concluded by the early finding (see Figure #3).

## **III. CONCLUSION**

With the confirmed root cause, the failed ESC was replaced. Both parameters are now included as part of the critical parameter list in FDC for monitoring which should prevent the re-occurrence of the same issue.

By utilizing the Trace Analytics solution, the engineer was able to quickly and accurately pinpoint the root cause of the wafer edge yield loss issue. This significantly shortened the root cause analysis time (from potentially days to hours) allowing him to take timely corrective actions and minimize further yield loss. In addition, the solution allowed a yield engineer to pull in and analyze all available sensor trace data in one place without the involvement of additional engineering resources (i.e.: the equipment engineer or the process engineer) which greatly simplified the root cause analysis process and increasing the productivity of all resources

-